2025年11月28日,随着搭载大容量缓存的X3D架构处理器在游戏应用中展现出显著性能优势,Intel正计划在下一代桌面级Nova Lake-S处理器上推出针对性技术方案,以应对市场竞争。

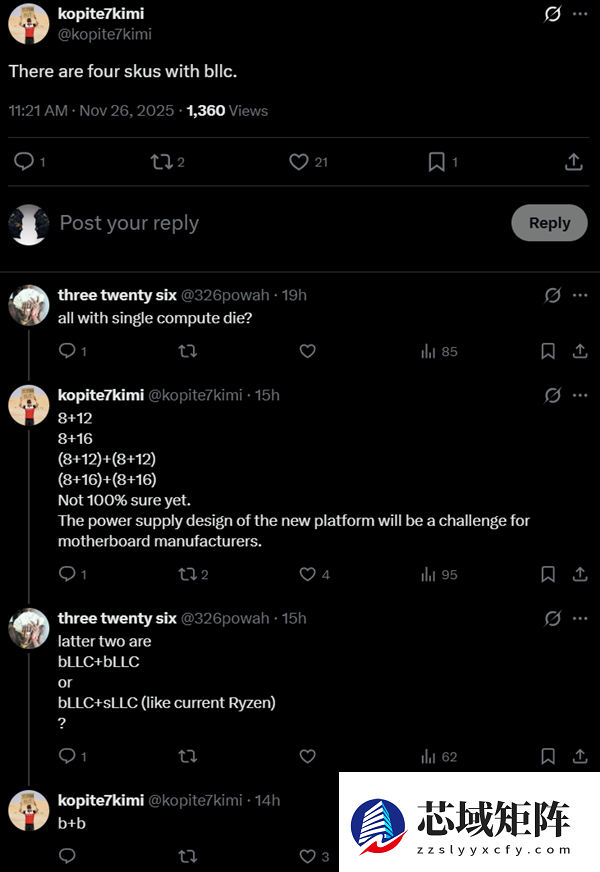

据最新信息显示,Nova Lake-S系列中至少将有四款型号配备名为bLLC(Big Last-Level Cache,大型末级缓存)的技术,通过大幅提升缓存容量来增强数据访问效率与整体性能表现。这些型号均采用不锁频设计,旨在为用户提供更高的性能释放空间和超频能力。

具体配置包括:

两款采用双计算模块(Compute Tile)设计的型号,分别集成两个8性能核+16能效核的单元,形成48个核心,并额外配备4个低功耗能效核(LPE),总计52核;另一款则由两个8+12核模块组成,提供40个主要核心,加上4个LPE核,总计44核。上述双模块型号均将搭载288MB bLLC缓存,每个计算模块各配备144MB。

此外,还有两款基于单计算模块的型号,分别配置为8性能核+16能效核(总计28核)和8性能核+12能效核(总计24核),并搭配144MB bLLC缓存。考虑到产品发布节奏,这类单模块版本更有可能作为首批上市型号推出。

由于bLLC带来了更高的功耗需求与瞬时电流波动,主板厂商在适配新一代LGA 1954接口平台时,需对供电设计进行全面升级,以确保稳定支持此类高负载、高缓存容量的处理器运行。

此次Intel大规模提升末级缓存容量,明显着眼于当前高端桌面市场中对延迟敏感型应用场景的优化,特别是游戏性能的竞争力补强,其技术方向可视为对竞品双层3D缓存架构的一种直接回应。据悉,后续也将有旗舰级产品采用类似堆叠缓存设计,进一步推动桌面处理器在响应速度和多任务处理上的边界拓展。